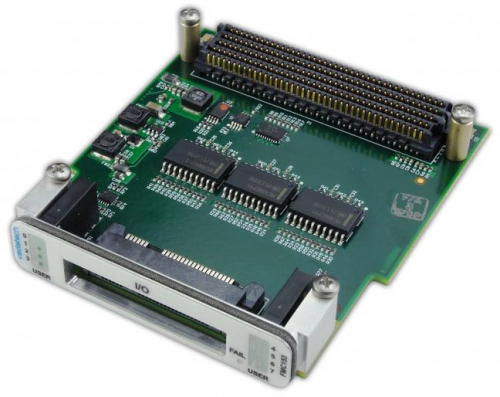

Description

The FMC150 is an FPGA Mezzanine Module per VITA 57 specification. The FMC150 has a 1PPS, 10 MHz Sine Wave or IRIG-B input.

The FMC150 provides the signals to the FPGA from which the firmware will decoded the IRIG-B data to set second’s year digits only.

The 3 inputs will be used along with front end parts and the FPGA to control a time-decade clock that will have 16 BCD digits: 1 digit of the year of the decade, 3 digits of days, 2 digits of hours, 2 digits of minutes, 2 digits of seconds and 6 digits of microseconds.

The module has on board Dual DPLL/IEEE 1588 with 1PPS Synchronize and Jitter Cleaner. The Dual DPLL synchronizes 1Hz to 750MHz, providing frequency with jitter cleaning of noisy references. Complies with ITU-T G.8286 and Telcordia GR-253. The module has Automatic and manual holdover, and reference switch over providing zero delay and hitless/phase buildout operation.

The Module outputs any clock output frequency thru its on board PLL.