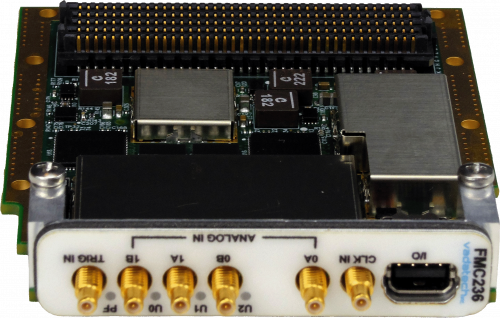

Description

The FMC210 is an FPGA Mezzanine Card per the VITA 57 specification with a high speedADC. The ADC converter utilizes the e2v EV10AS150B device which has a high linearityADC. The module has a super low phase noise RF PLL Synthesizer for sampling.

The ADC device has single Tone Performance in 1st Nyquist (–1 dBFS): ENOB = 8.0 bit,SFDR = –57 dBFS at 2.6 GSPS, Fin = 495 MHz and ENOB = 7.9 bit , SFDR = –57 dBFS at2.6 GSPS, Fin = 1295 Mhz, with the single Tone Performance in 2nd Nyquist (–3 dB): ENOB= 7.9 bit, SFDR = –59 dBFS at 2.6 GSPS, Fin = 2,595 MHz.

The module has a low Bit Error Rate (BER) of 10 to -12 at 2.6 GSPS with no missing codesat 2.6 GSPS, 1st and 2nd Nyquist.