Description

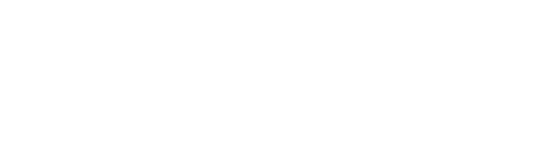

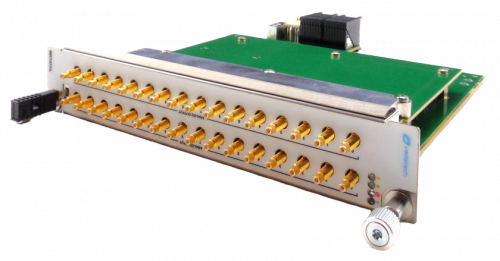

The AMC521 utilizes eight dual channel ADS42JB69 ADC converters at 250 MSPS with 16-bit resolution for 16 high sampling rate channels. In addition the module has eight 16-bit Successive Approximation Register (SAR) based on TI ADS8568 ADC at a lower sampling rate for measurements up to 650 KSPS. There are also 24 LVDS I/O which can be used for Clock In/Out, Trig In/Out or GPIO.

The AMC521 has an M-LVDS Cross Bar Switch (CBS) for clock distribution which allows clocking from front panel, backplane, or on-board VCXO. The clock outputs to the backplane for distribution to other modules. The AMC521 has a Virtex-7 FPGA with option of 415T or 690T in FFG1158 package.

The AMC ports 4-7 and 8-11 are routed to the FPGA for PCIe, XAUI, SRIO, or other SerDes protocols. AMC ports 0, 1 and 2, 3 are also routed to the FPGA for base channel and storage point-to-point connectivity.