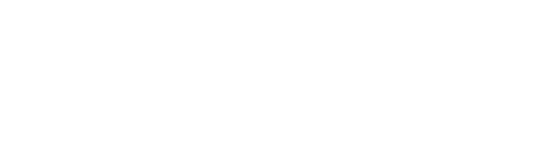

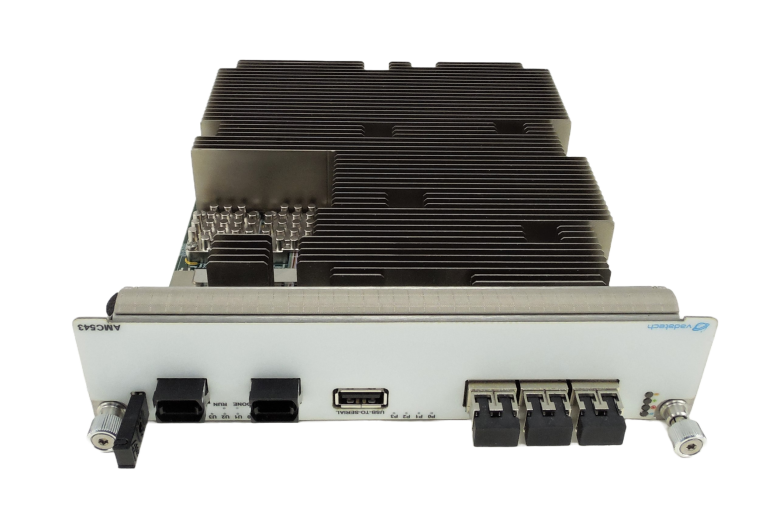

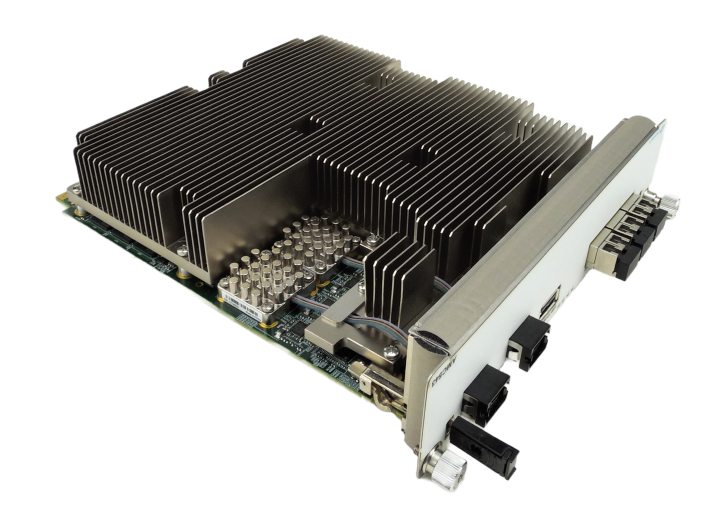

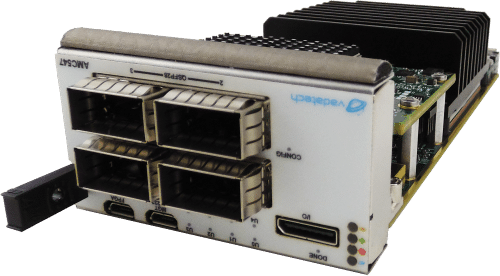

Description

The AMC543 incorporates the Xilinx Zynq® UltraScale+ XCZU19EG FPGA with Dual TI 66AK2H14 DSP devices. This re-configurable FPGA connects directly to the backplane allowing the core to interface to a host with multiple protocols such as 10/40GbE, PCIe, SRIO and/or Aurora. Dual multicore Digital Signal Processors (DSP) 66AK2H14 connect to the FPGA via PCIe x2, SRIO x4, GbE, EMIF16 (local bus of the DSP) as well as 10GbE thru the on board 10GbE Switch. The FPGA also interfaces to the AMC FCLKA and TCLKA/B/C/D and has dual 8GB of 64-bit DDR4 memory.

Further AMC ports 12-15 and 17-20 are routed to the FPGA. Ports 17-20 have options to be routed as SERDES or M-LVDS.

The Dual DSP devices interconnect with each other through two x4 HyperLink as well as GPIO interface between the two DSP. Each DSP has 8 GB of DDR-3 memory with ECC. Each DSP also routes 10GbE thru the front panel via SFP+ style optics.

The AMC543 has GbE on Ports 0/1 per AMC.2, Ports 2/3 per AMC.3, PCIe Gen3 dual x4 or x8, dual SRIO/10GbE/40GbE per AMC.1/ AMC.2/ AMC.4 specifications to ports 4-11. Ports 12-15 as SERDES (option) and 17-20 as M-LVDS or SERDES (option) can also route to the FPGA.

The AMC543 has an Ethernet switch which interconnects the dual DSP, FPGA and supports a 10GbE front panel via SFP+ style optics.