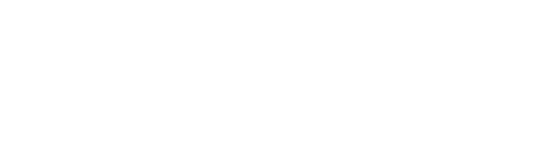

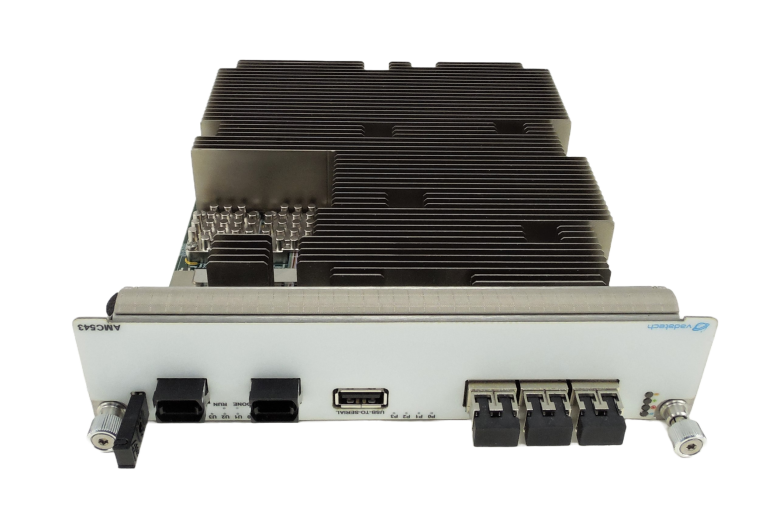

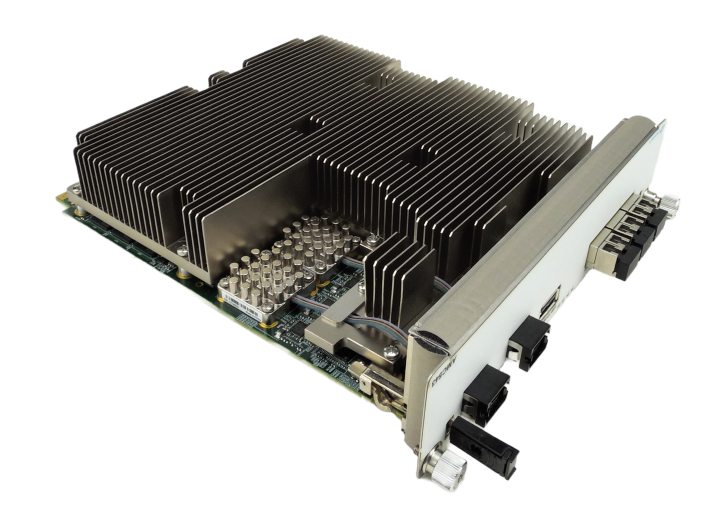

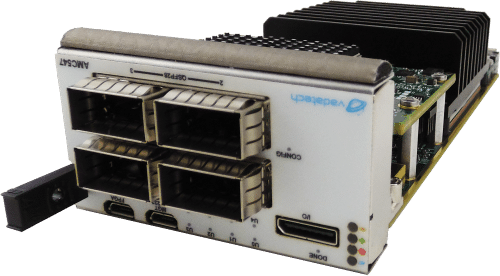

Description

The AMC543 incorporates the Xilinx Zynq® UltraScale+ XCZU19EG FPGA with Dual TI 66AK2H14 DSP devices. This re-configurable FPGA connects directly to the backplane allowing the core to interface to a host with multiple protocols such as 10/40GbE, PCIe or SRIO. Dual multicore Digital Signal Processors (DSP) 66AK2H14 connect to the FPGA via PCIe x2, and SRIO x4. The FPGA also interfaces to the AMC FCLKA and TCLKA/B/C/D and has dual 8GB of 64-bit DDR4 memory.

The Dual DSP device interconnect with each other through two x4 HyperLink. Each DSP has 8 GB of DDR-3 memory with ECC.

The AMC543 has GbE on Ports 0/1 per AMC.2, Ports 2/3 per AMC.3, PCIe Gen3/SRIO/10GbE dual x4 or single x8 on Ports 4-11 per AMC.1/ AMC.2/ AMC.4 specifications. Ports 12-15 as SERDES (option) and 17-20 as MLVDS or SERDES (option) can also routed to the FPGA.

The AMC543 has an Ethernet switch which interconnects the dual DSP, FPGA and supports a 10GbE front panel.